ผลต่างระหว่างรุ่นของ "Com sys lab/testing ALU"

Jittat (คุย | มีส่วนร่วม) (→Latch) |

Jittat (คุย | มีส่วนร่วม) (→Latch) |

||

| แถว 10: | แถว 10: | ||

* sc_in_clk clk; | * sc_in_clk clk; | ||

| − | + | โดย latch จะเปลี่ยนค่า output b ให้เท่ากับ input a เมื่อ clk เปลี่ยนค่าจาก 0 -> 1 (positive edge triggered) นอกจากนี้ใน module ให้เพิ่ม method get และ set สำหรับอ่านและเขียนค่า b โดยตรงด้วย (เพื่อเป็นการตั้งค่าเริ่มต้น) | |

| − | + | '''Hint:''' ในการเลือก positive edge trigger นั้น ตอนใส่ clk ใน sensitive ให้ใส่ clk.pos() แทน | |

| + | |||

| + | '''หมายเหตุ:''' ที่ลงท้ายว่า 4 เพราะจะเป็น latch 4 บิต (ในงานถัด ๆ ไปจะต้องทำ latch 8 บิตด้วย สำหรับ program counter) | ||

จากนั้นให้นำ latch ไปต่อกับ ALU เพื่อทดสอบการทำงาน โดยมีแผนภาพการเชื่อมต่อดังนี้ (ด้านล่างเป็นตัวอย่างการทดสอบ op = 0 (add) ) | จากนั้นให้นำ latch ไปต่อกับ ALU เพื่อทดสอบการทำงาน โดยมีแผนภาพการเชื่อมต่อดังนี้ (ด้านล่างเป็นตัวอย่างการทดสอบ op = 0 (add) ) | ||

รุ่นแก้ไขเมื่อ 01:18, 22 มิถุนายน 2559

- จากวิชา com sys lab

ในส่วนนี้เราจะหัดใช้ latch เพื่อทดสอบ ALU จากนั้นเราจะลองนำ ALU มาต่อกับ register file (มีให้) เพื่อทดลองส่งสัญญาณควบคุมการทำงานของระบบ

Latch

สร้าง module latch4 ที่มี port ดังนี้:

- sc_in<sc_uint<4> > a;

- sc_out<sc_uint<4> > b;

- sc_in_clk clk;

โดย latch จะเปลี่ยนค่า output b ให้เท่ากับ input a เมื่อ clk เปลี่ยนค่าจาก 0 -> 1 (positive edge triggered) นอกจากนี้ใน module ให้เพิ่ม method get และ set สำหรับอ่านและเขียนค่า b โดยตรงด้วย (เพื่อเป็นการตั้งค่าเริ่มต้น)

Hint: ในการเลือก positive edge trigger นั้น ตอนใส่ clk ใน sensitive ให้ใส่ clk.pos() แทน

หมายเหตุ: ที่ลงท้ายว่า 4 เพราะจะเป็น latch 4 บิต (ในงานถัด ๆ ไปจะต้องทำ latch 8 บิตด้วย สำหรับ program counter)

จากนั้นให้นำ latch ไปต่อกับ ALU เพื่อทดสอบการทำงาน โดยมีแผนภาพการเชื่อมต่อดังนี้ (ด้านล่างเป็นตัวอย่างการทดสอบ op = 0 (add) )

+-------+ +-------+ +->| LATCH |------->|a c|------+ | | | | ALU | | | +-------+ 1-->|b op | | | | +-------+ | | clk | | | 0 | +----------------------------------+

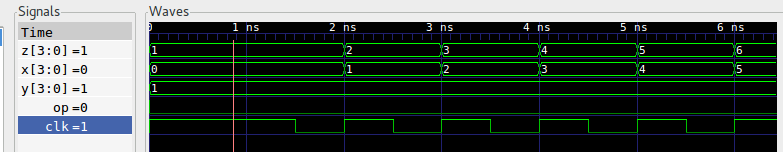

ด้านล่างเป็นตัวอย่าง signal ที่ควรเห็น (y=1 เอาหนึ่งไปบวกตลอด; ผลลัพธ์อยู่ที่ z) ควรเพิ่ม signal ของ zero flag ด้วย

อ่านเพิ่มเติม: การใช้งาน clock