Com sys lab/control unit that works with registers

- มาจาก com sys lab

ใช้เทมเพลตใหม่ ในแบบฝึกหัดนี้ control unit จะเชื่อมโยงกับส่วนอื่น ๆ ซับซ้อนขึ้น อ่าน instruction set ของ CPU ได้ที่นี่

สำหรับปฏิบัติการนี้ เราจะทยอยเพิ่มความสามารถของ Control Unit ให้รองรับคำสั่งที่ทำงานหลัก ๆ บน register เพื่อการทดสอบสามส่วนแรก เราจะกำหนดให้ register $1 มีค่าเป็น 1 ก่อน (เพราะจะได้มีค่าคงที่เอาไว้ใช้ประมวลผล) เราจะใช้คำสั่ง LDAI เพื่อแก้ข้อจำกัดนี้ในส่วนที่ 4

ดาวน์โหลดไฟล์ template ได้ที่นี่ https://theory.cpe.ku.ac.th/~jittat/com-sys-lab/cpureg.zip

หมายเหตุ มีการแก้ op-code format ของ ADD และ SUB จากแลบครั้งก่อน (เพื่อไม่ให้ชนกับ NOP = 0x00)

เนื้อหา

โครงสร้างของระบบ

ส่วนที่ 1: Load to $0, Store from $0

ให้แก้ส่วน control unit ให้รองรับคำสั่ง LDA และ STA

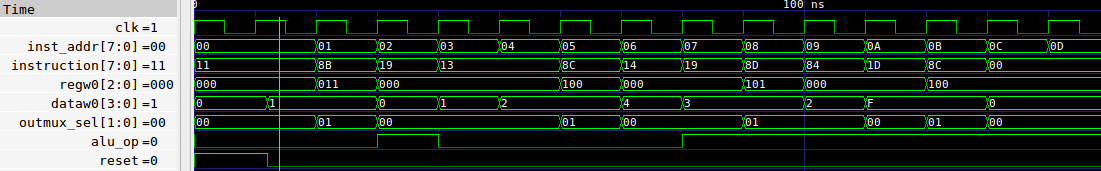

เพื่อทดสอบการออกแบบ control unit ในส่วนนี้เราจะใช้โค้ดในการเตรียมค่า register และคำสั่งใน instruction memory ดังด้านล่าง

// set register $1 = 1

reg.set(1,1);

// set instruction memory

rom.set(0,0x11); // ADD $1 $0 = 1

rom.set(1,0x8b); // STA $3 $3 = 1

rom.set(2,0x19); // SUB $1 $0 = 0

rom.set(3,0x13); // ADD $3 $0 = 1

rom.set(4,0x13); // ADD $3 $0 = 2

rom.set(5,0x8c); // STA $4 $4 = 2

rom.set(6,0x14); // ADD $4 $0 = 4

rom.set(7,0x19); // SUB $1 $0 = 3

rom.set(8,0x8d); // STA $5 $5 = 3

rom.set(9,0x84); // LDA $4 $0 = 2

rom.set(10,0x1d); // SUB $5 $0 = -1 = 0x0f

rom.set(11,0x8c); // STA $4 $4 = 0xf

ตัวอย่าง signal การทำงานดูด้านล่าง (ในการทดสอบ สังเกตว่าเราสามารถไล่การทำงานจาก regw0 และ dataw0 เพื่อดูลำดับการเขียนค่าลงใน register file ได้)

ส่วนที่ 2: Unconditional short jump

ให้แก้ส่วน control unit ให้รองรับคำสั่ง JMP

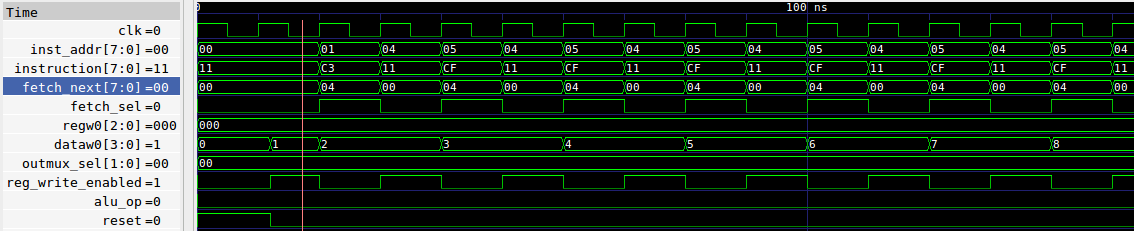

เพื่อทดสอบการออกแบบ control unit ในส่วนนี้เราจะใช้โค้ดในการเตรียมค่า register และคำสั่งใน instruction memory ดังด้านล่าง

// set register $1 = 1

reg.set(1,1);

// set instruction memory

rom.set(0,0x11); // ADD $1 $0 = 1

rom.set(1,0xc3); // JMP 3 PC = 4

rom.set(2,0x19); // SUB $1

rom.set(3,0x89); // STA $1

rom.set(4,0x11); // ADD $1 $0 = 2,3,4,...

rom.set(5,0xcf); // JMP -1 PC = 4

ตัวอย่าง signal การทำงานดูด้านล่าง (ในการทดสอบ สังเกตว่าเราสามารถไล่การทำงานจาก inst_addr, regw0, และ dataw0 เพื่อดูลำดับการเขียนค่าลงใน register file ได้)

ส่วนที่ 3: Jump if zero และ NOP

ให้แก้ส่วน control unit ให้รองรับคำสั่ง NOP และ JZ

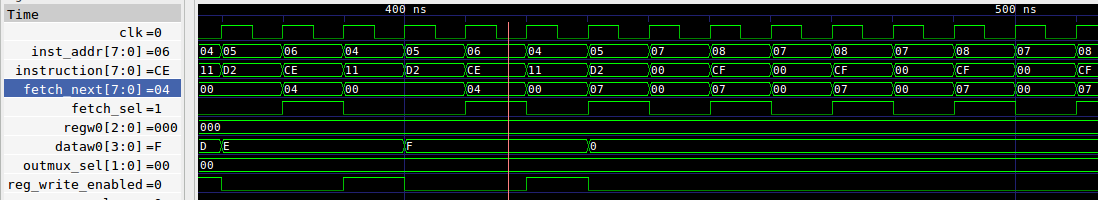

เพื่อทดสอบการออกแบบ control unit ในส่วนนี้เราจะใช้โค้ดในการเตรียมค่า register และคำสั่งใน instruction memory ดังด้านล่าง

// set register $1 = 1

reg.set(1,1);

// set instruction memory

rom.set(0,0x11); // ADD $1 $0 = 1

rom.set(1,0xc3); // JMP 3 PC = 4

rom.set(2,0x19); // SUB $1

rom.set(3,0x89); // STA $1

rom.set(4,0x11); // ADD $1 $0 = 2,3,4,...

rom.set(5,0xd2); // JZ 2 PC = 7 if $0 = 0

rom.set(6,0xce); // JMP -2 PC = 4

rom.set(7,0x00); // NOP

rom.set(8,0xcf); // JMP -1 PC = 7

ตัวอย่าง signal การทำงานดูด้านล่างซึ่งแสดงส่วนของการทำงานที่มีการสั่ง JZ (เมื่อ $0=0) และลูประหว่างคำสั่งที่ตำแหน่ง 7 และ 8 (ในการทดสอบ สังเกตว่าเราสามารถไล่การทำงานจาก inst_addr, regw0, และ dataw0 เพื่อดูลำดับการเขียนค่าลงใน register file ได้)

ส่วนที่ 4: Load immediate

ให้แก้ส่วน control unit ให้รองรับคำสั่ง LDAI

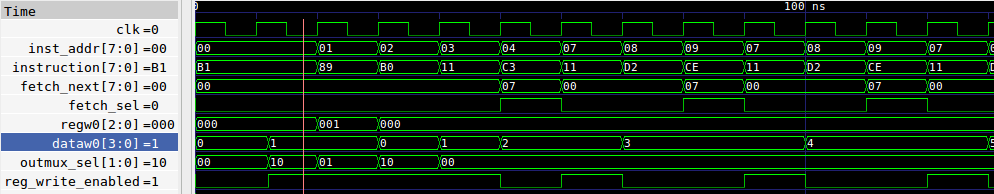

เพื่อทดสอบการออกแบบ control unit ในส่วนนี้เราจะตัดโค้ดที่ใช้เตรียมค่า register ออก และใช้คำสั่ง LDAI ในการกำหนดค่าเริ่มต้น โดยมีคำสั่งใน instruction memory ดังด้านล่าง

// set instruction memory

rom.set(0,0xb1); // LADI 1 $0 = 1

rom.set(1,0x89); // STA $1 $1 = 1

rom.set(2,0xb0); // LADI 0 $0 = 0

rom.set(3,0x11); // ADD $1 $0 = 1

rom.set(4,0xc3); // JMP 3 PC = 7

rom.set(5,0x19); // SUB $1

rom.set(6,0x89); // STA $1

rom.set(7,0x11); // ADD $1 $0 = 2,3,4,...

rom.set(8,0xd2); // JZ 2 PC = 10 if $0 = 0

rom.set(9,0xce); // JMP -2 PC = 7

rom.set(10,0x00); // NOP

rom.set(11,0xcf); // JMP -1 PC = 10

ตัวอย่าง signal การทำงานดูด้านล่างซึ่งแสดงสัญญาณในตอนเริ่มต้น สังเกตสัญญาณ dataw0, regw0, และ outmux_sel